# PI3EQX501(I) PI3EQX501(I) EVB Rev.A User Manual

By YT Tso, Anne Wu and Jessy Chen

### • Introduce:

PI3EQX501(I) is a 1-channel low power high performance 5.0Gbps signal ReDriver designed for USB3.0 protocol. The device provides programmable Equalization (EQ) and De-Emphasis (DE) to optimize performance over a variety of physical mediums by reducing Inter-Symbol Interference (ISI)

## Quick Start — For Default Setting:

To start-up the PI3EQX501(I) EVB, complete the following steps: For TX test,

- 1. Check the head pin status and follow Table 1

- 2. Connect the JP4 on EVB to PC's USB3.0 port through a USB3.0 Type A to B cable.

- 3. Plug the USB3.0 device into EVB USB Type-A connector JP6 through USB3.0 cable

#### For RX test,

- 4. Check the head pin status and follow Table 1

- 5. Connect the JP10 on EVB to PC's USB3.0 port through a USB3.0 Type A to B cable.

- 6. Plug the USB3.0 device into EVB USB Type-A connector JP11 through USB3.0 cable

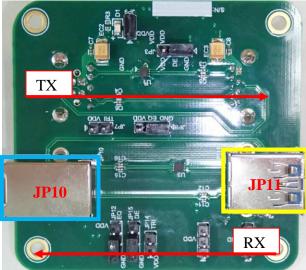

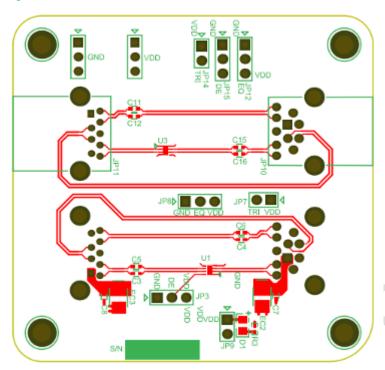

Figure 1(a) Top view of PI3EQX501(I) EVB

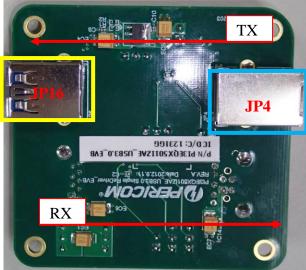

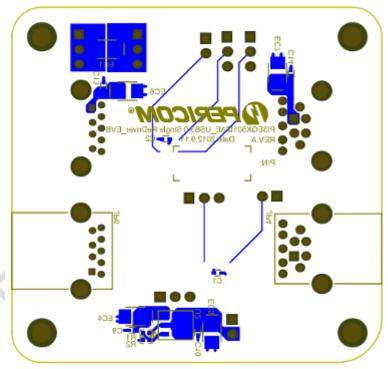

Figure 1(b) Bottom view of PI3EQX501(I) EVB

Table 1--Header pin is set as defaulted on EVB.

| Header pin<br># | Pin name for PI3EQX7841 | Switch status | Remark                                               |  |

|-----------------|-------------------------|---------------|------------------------------------------------------|--|

| JP3             | DE                      | Short to GND  | De-emphasis setting on TX side                       |  |

| JP7             | TRI                     | Open          | Normal Operating mode on TX side-> RX.Detect enabled |  |

| JP8             | EQ                      | Short to GND  | Equalizer setting on TX side                         |  |

| JP9             | VDD                     | Short         | Power on PI3EQX501(I) both TX and RX sides.          |  |

| JP12            | EQ                      | Open          | Equalizer setting on RX side                         |  |

| JP14            | TRI                     | Open          | Normal Operating mode on RX side-> RX.Detect enabled |  |

| JP15            | DE                      | Short to GND  | De-emphasis setting on RX side                       |  |

Equalizer setting:

| Header pin<br># | Pin name for PI3EQX501(I) |    | Switch status | Remark            |  |               |      |

|-----------------|---------------------------|----|---------------|-------------------|--|---------------|------|

|                 | EQ                        | TX | Short to GND  | Equalizer setting |  |               |      |

| JP8             |                           |    |               | EQ                |  | @ 2.5GHz      | (O   |

|                 |                           |    |               | 0                 |  | 3 dB          | 16   |

| JP12            | EQ                        | RX | Short to GND  | open              |  | 6dB (Default) | 'O'. |

|                 |                           |    |               | 1                 |  | 9dB           | 10,  |

De- emphasis setting:

| Header pin<br># | Pin name for PI3EQX501(I) |    | Switch status              | Remark |             |  |

|-----------------|---------------------------|----|----------------------------|--------|-------------|--|

| JP3             | JP3 DE TX Open            |    | Output de-emphasis setting |        |             |  |

|                 |                           |    | •                          | DE     | De-emphasis |  |

| JP15            | DE                        | RX | Open                       | 0      | 0 dB        |  |

|                 |                           |    |                            | open   | -3.5 dB     |  |

|                 |                           |    |                            | 1      | -6 dB       |  |

JP12 short to GND: EQ=3dB on RX side

JP15 short to GND: DE=0dB on RX side

JP8 short to GND: EQ=3dB on TX side

JP3 short to GND: DE=0dB on TX side

JP9 short: Power on PI3EQX501 (I)

CJ1 117-ADJ

# **PCB** Layout

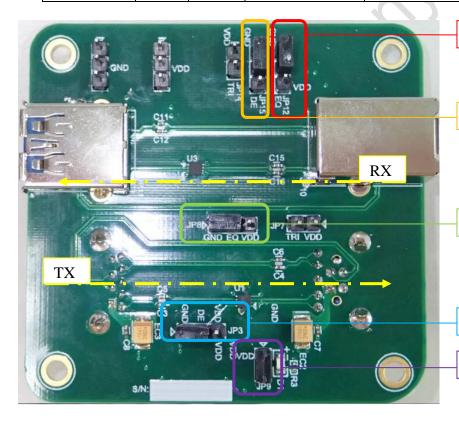

Figure 2, Top view of PI3EQX501(I) EVB Layout

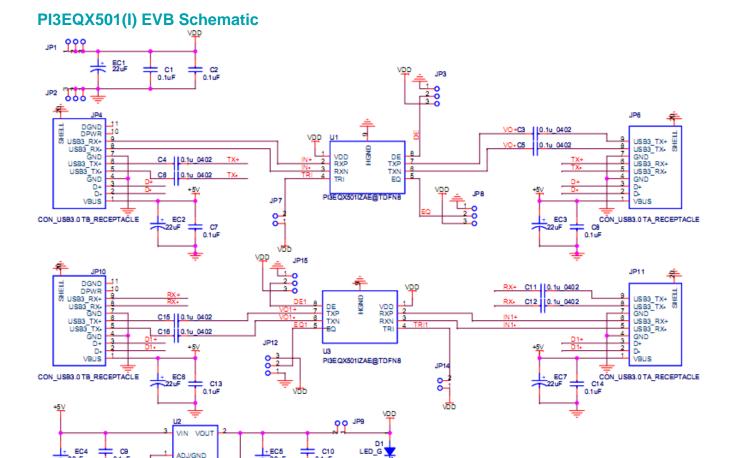

Figure 3, Bottom view of PI3EQX501(I) EVB Layout