### PI2EQX6811ZDE Evaluation Board Rev.B User Guide Nov.16, 2011

#### Contents

#### Introduction

- Board Operation

- Power options

- Device configuration

- System connection

- Power-on sequence

#### Board Design Information

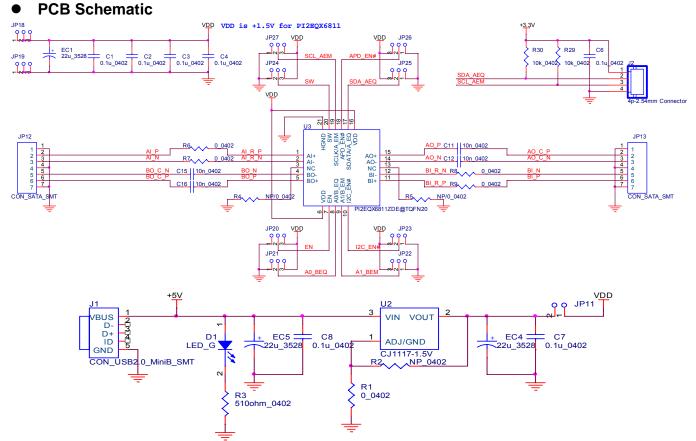

- PCB Schematic

- PCB Layout Reference

- PCB BOM List

#### Introduction

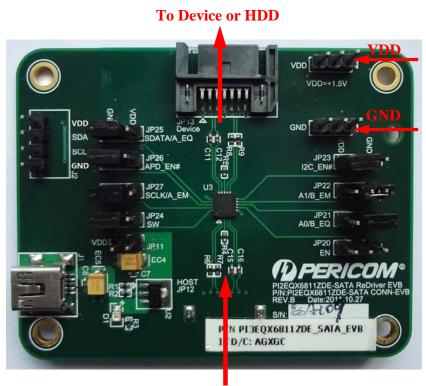

PI2EQX6811ZDE Evaluation Board is designed to allow convenient testing of its operation and features. This board can work with readily available SATA and eSATA cables for easy connection to SATA3.0 HDD, SSD, OMD storage components and PC system hosts.

This board allows the PI2EQX6811ZDE device to be powered in +1.5V directly from external power, or 5V with a mini-USB connector provided to convert.

This User Guide describes the setup, configuration and operation of PI2EQX6811ZDE Eval Board Rev.B. Figure1 provides a top view of PI2EQX6811ZDE Eval Board Rev.B, and Figure2 is bottom view of the board.

Figure1. Top view of PI2EQX6811ZDE Eval board Rev.A

# Application\_Note

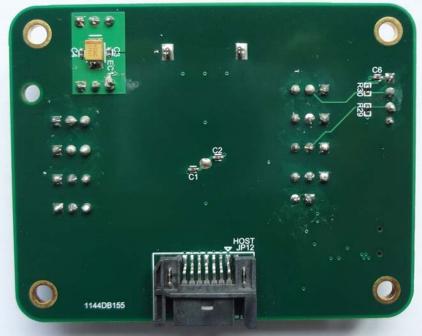

Figure2. Bottom view of PI2EQX6811ZDE Eval board Rev.A

#### **Board Operation**

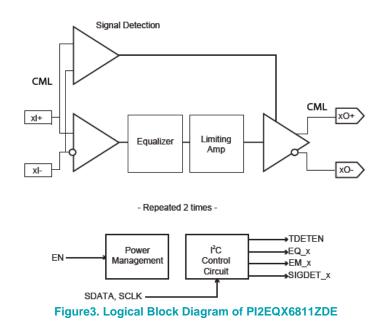

PI2EQX6811ZDE is a 1-port (2-channel), bi-directional, signal SATA3.0 re-driver to provide indication when the load is connected to HOST or Device. Figure3 shows the logical block diagram of PI2EQX6811ZDE. Two channels of the PI2EQX6811ZDE are fully independent in operation and configuration by I2C function. Channel configuration of output pre-emphasis, output swing and input equalization must be set appropriately to match the attached cable/trace length and type.

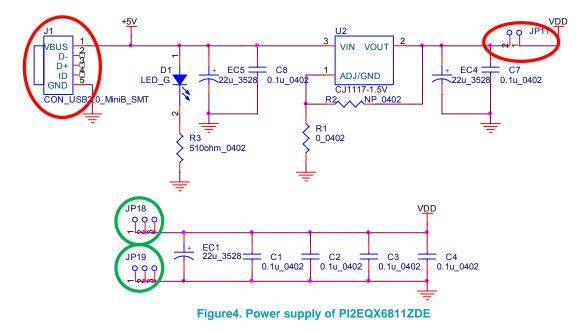

The PI2EQX6811ZDE Evaluation Board provides the options for supplying +1.5V directly or +5V power from mini-USB connector. Figure 4 circles the important connections.

Application

- 1) Using the +5V power supplied by miniUSB connector (J1). The on-board LDO down-steps the voltage to +1.5V. When using this source, note that jumper JP11 must be shorted (populated).

- 2) Using +1.5V power input directly by JP18 power pin header and JP19 ground pin header. When using this method, JP11 must be open.

- 3) For PI3EQX6801ZDE power supply, the evaluation board is shipped from the default with +1.5V from externally power supply.

#### • Device Configuration

The PI2EQX6811ZDE ReDriver supports Pre-emphasis, swing adjustment and input equalization for optimum operation and signal margins.

PI2EQX6811ZDE provides two ways configuration controls depending on the state of the I2C\_EN# pin.

- When I2C\_EN# is set to HIGH (JP23 to VDD), the configuration input pins set the configuration operating state and changes to these control pins will change the operating I2C\_EN#. For pin configurations, there are some configuration values to be selected only.

- When I2C\_EN# pin is set to LOW (JP23 to GND), reprogramming of these control registers via I2C is allowed. For I2C configurations, all the configuration values can be used by I2C as default configuration on EVB.

Table1 shows the pin functions for pin control and I2C control.

| PIN NAME           | PIN Control FUNCTION                                                                                                                                                              | I2C Control Function            |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| P7:EN              | With Internal 100k-ohm pull-up resistor<br>High: Normal Operation                                                                                                                 | Same as Pin control function    |

| P8:A0/B_EQ         | Low: Dower Power Mode<br>Input Equalization for Channel B<br>Tri-level control<br>JP21 Input Equalization for Channel B<br>GND 8dB<br>Open 4dB<br>VDD 16dB                        | I2C Programmable address bit A0 |

| P9:A1/B_EM         | Pre-emphasis control for Channel B<br>Tri-level control<br>JP22 Input Equalization for Channel B<br>GND 2dB<br>Open 0dB<br>VDD 3.5dB                                              | I2C Programmable address bit Al |

| P10:I2C_EN#        | I2C Enable<br>High: pin control<br>Low: I2C control                                                                                                                               | Same as Pin control function    |

| P17:<br>SDATA/A_EQ | Input Equalization for Channel A<br>Tri-level control by JP25                                                                                                                     | I2C Data Line                   |

| P18:APD_EN#        | Setting Value same as D8<br>Auto slumber mode Enable<br>High: disable<br>Low: enable                                                                                              | Don't Care                      |

| P19:<br>SCLK/A_EM  | Pré-emphasis control for Channel A<br>Tri-level control by JP27                                                                                                                   | I2C Clock Line                  |

| ₽20∶SW             | Setting Value same as D9   Output Swing control for Channel A&B   Tri-level control   JP24 Output Swing for Channel A&B   mV(Vtx diff pp) at 3Gb/s   GND 667   Open 533   VDD 900 | Don't Care                      |

#### 1) Pin Configurations

Configuration begins with I2C\_EN# pin with JP23, which must be connected to VDD. The EN pin of the PI2EQX6811ZDE has an internal 200K pull-up resistor to define a high level default (JP20 Open) for normal operation.

When EN pin is shorted to GND (**JP20** is shorted to GND), device operation is disabled. This is useful for checking PI2EQX6811ZDE disabled-state power consumption. Figure5 is pin strap configuration for pin headers.

# Application\_Note

Figure5. Pin Strap Configuration of PI2EQX6811ZDE

#### • Input Equalizer Setting

Input equalizer setting has P17 (A\_EQ) and P18 (B\_EQ) tri-level configuration by JP25 and JP21. So it is available with 3 values in **Blue** color in Table1 below.

#### Output Pre-emphasis Setting

Output Pre-emphasis setting has P19 (A\_EM) and P9 (B\_EM) tri-level configuration by JP27 and JP22. Table1 shows its selectable setting values.

#### • Output Swing Setting

Output Swing setting has P20 (SW) tri-level configuration by JP24. Table1 shows its selectable setting values.

#### • Auto-slumber Mode Enable Setting

Auto-slumber mode enable setting has P18 (APD\_EN#) configuration by JP26. When JP26 is connected to GND, auto-slumber mode will be enabled, but it is connected to VDD, auto-slumber mode will be disabled.

#### 2) I2C Configuration

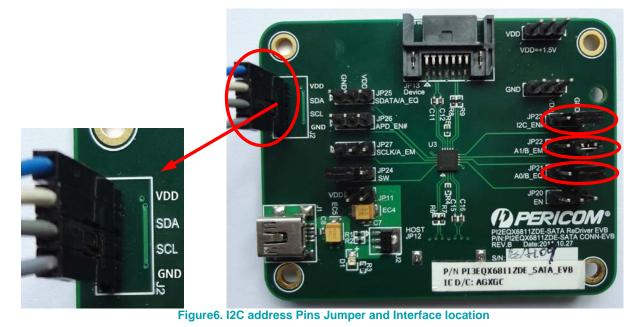

On PI2EQX6811ZDE EVB, I2C\_EN# pin (JP23) is shorted to GND on EVB, I2C configuration is enabled for all the setting as default. And P8 (JP21, A0) and P9 (JP22, A1) pins are also shorted to GND as default I2C address-**C0**. Figure6 is their locations on EVB and I2C interface connector definition and location.

## Application\_Note

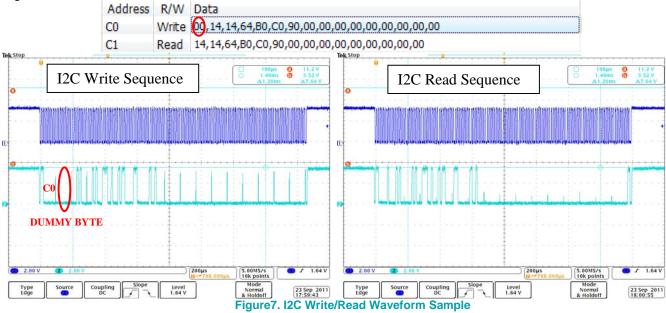

For PI2EQX6811ZDE's I2C interface, it is compliant with 3.3V power. Figure7 is read/write waveform sample at the register value below for the reference.

**NOTE that there is one dummy byte in Write Sequence.** For detail I2C register description, please refer to **Page7-10** in datasheet.

#### 3) Board Connection

Figure8 is board connections for the reference.

From Host Figure8. Board Connection

#### • System Connection

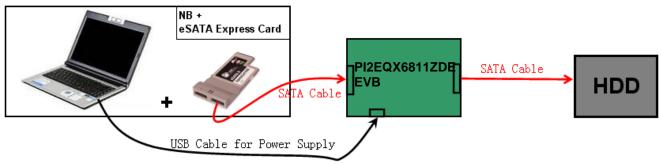

The diagrams below show some example system test setups with the PI2EQX6811ZDE Eval Board.

Figure9 shows the connection using a NB PC and eSATA Express Card. Note that many notebooks PCs already offer an eSATA port which can be used as the test signal source without the add-in card.

Figure9. eHDD connection Test Setup using NB+eSATA Express Card with PI2EQX6811ZDE Eval Board

Application\_Note

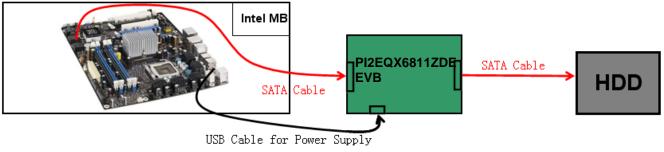

#### Figure10 shows the connection using Intel MB

Figure 10. internal HDD connection Test Setup using Intel MB with PI2EQX6811ZDE Eval Board

#### Power-on Sequence

It is recommended as good practice, that all system components be powered off while connections and configuration settings are made. There is no specific power-on sequence required when applying power to the PI2EQX6811ZDE Eval Board. When connected to the system and powered by USB as shown above, then all devices will power-up together.

If the host PC and/or HDD are powered on, while the Eval Board is off, there will be no damage to the PI2EQX6811ZDE under typical conditions. If the Eval Board is then powered on, the system will generally detect the SATA HDD as a hot-plug event, and the HDD will begin to operate properly. Note that some PC systems offer BIOS control over hot plug events, and if the HDD is not recognized, this BIOS setting is the most likely cause and should be changed. When connecting to the system as shown above, all devices will power on together and avoid this BIOS issue.

### Application\_<sub>Note</sub>

**Board Design Information**

#### • PCB Layout Reference

a. Stack Up:

| Layer # | Plane       | Material type                | mil |

|---------|-------------|------------------------------|-----|

|         | Solder Mask |                              | 0.4 |

| Layer 1 | Signal      |                              | 1.9 |

|         | Prepreg     | Prepreg 1080<br>Prepreg 2116 | 7.3 |

| Layer 2 | Gnd         |                              | 1.2 |

|         | Core        |                              | 44  |

| Layer 3 | Power       |                              | 1.2 |

|         | Prepreg     | Prepreg 2116<br>Prepreg 1080 | 7.3 |

| Layer 4 | Signal      |                              | 1.9 |

|         | Solder Mask |                              | 0.4 |

- b. Isolation Spacing = 30 mil

- c. Width & Spacing (W/S) of  $100\Omega$  Differential Trace = 10 / 9 mil

#### PCB BOM List

| Reference                 | Description                      | Package | Qty |

|---------------------------|----------------------------------|---------|-----|

| U2                        | LM3674-1.5V                      | SOT23-5 | 1   |

| U3                        | PI2EQX6811ZDE@TQFN20             | TQFN20  | 1   |

|                           | PCB, PI2EQX6811ZDE-SATA ReDriver |         |     |

| Bare PCB                  | Rev.B                            | PCB     | 1   |

| D1                        | LED                              | 0805    | 1   |

| JP12,JP13                 | SATA L-type connector            | L-type  | 2   |

| J2                        | 4p-2.54mm Connector              | 2.54mm  | 1   |

| J1                        | miniUSB connector                | B-type  | 1   |

| JP11                      | 2PIN HEADER                      | 2.54mm  | 1   |

| JP18,JP19,JP20,JP21,JP22, |                                  |         |     |

| JP23,JP24,JP25,JP26,JP27  | 3PIN HEADER                      | 2.54mm  | 10  |

| C11,C12,C15,C16           | Ceramic Capacitor, 10nF          | 0402    | 4   |

| C1,C2,C3,C4,C6,C7,C8      | Ceramic Capacitor, 0.1uF         | 0402    | 7   |

| EC1,EC4,EC5               | Tan cap, 22u                     | 3528    | 3   |

| R3                        | Chip Resistor, 510ohm            | 0402    | 1   |

| R29,R30                   | Chip Resistor, 10Kohm            | 0402    | 2   |

| R1,R6,R7,R8,R9            | Chip Resistor, 0ohm              | 0402    | 5   |

#### History

Version 1.0

Original Version

Nov 16, 2011